《《計(jì)算機(jī)系統(tǒng)結(jié)構(gòu)》綜合自測(cè)題1》由會(huì)員分享����,可在線閱讀����,更多相關(guān)《《計(jì)算機(jī)系統(tǒng)結(jié)構(gòu)》綜合自測(cè)題1(2頁(yè)珍藏版)》請(qǐng)?jiān)谘b配圖網(wǎng)上搜索。

1����、精品文檔,僅供學(xué)習(xí)與交流�,如有侵權(quán)請(qǐng)聯(lián)系網(wǎng)站刪除000000414姓名_ 專業(yè)名稱_班號(hào)_學(xué)號(hào)_教學(xué)中心_ 密 封 線 電子科技大學(xué)網(wǎng)絡(luò)教育考卷(A1卷)(20 年至20 學(xué)年度第 學(xué)期)考試時(shí)間 年 月 日(90分鐘) 課程 計(jì)算機(jī)系統(tǒng)結(jié)構(gòu) 教師簽名 文軍 大題號(hào)一二三四五六七八九十合 計(jì)得 分注意:所有題目的答案均填涂在答題卡上,寫(xiě)在本試卷上的答案無(wú)效一�、填空題(將下列各題正確的答案填入下面的括號(hào)中,每空1分����,共20分。)1. Flynn分類法是按指令流和數(shù)據(jù)流的不同組織方式���,將計(jì)算機(jī)系統(tǒng)結(jié)構(gòu)分為( )、( )���、( )��、( ) 四類�。2. 流水線沖突有三種類型:( )、( )����、( )。3.

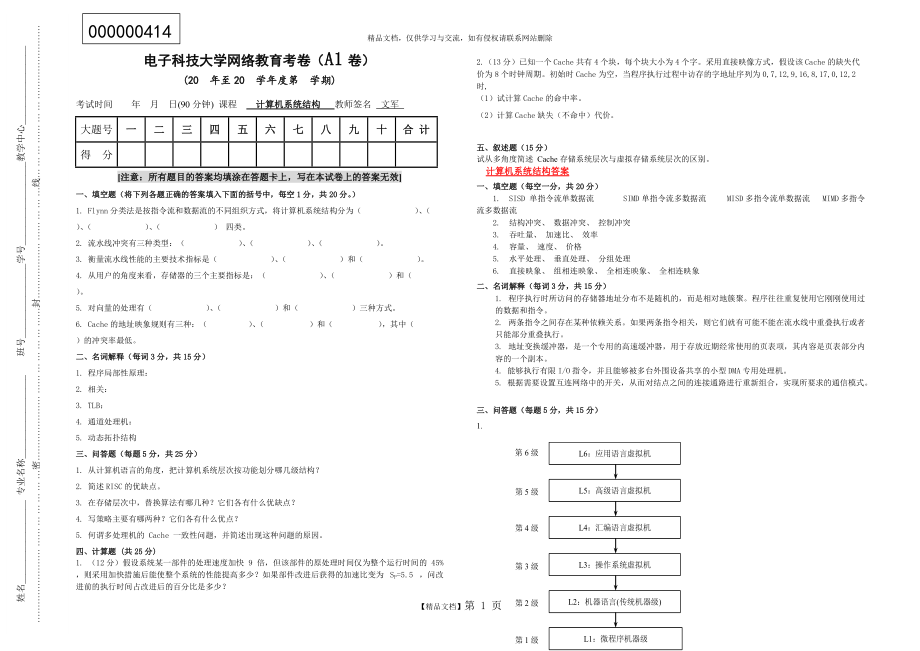

2�����、 衡量流水線性能的主要技術(shù)指標(biāo)是( )��、( )和( )����。4. 從用戶的角度來(lái)看,存儲(chǔ)器的三個(gè)主要指標(biāo)是:( )����、( )和( )。5. 對(duì)向量的處理有( )��、( )和( )三種方式���。6. Cache的地址映象規(guī)則有三種:( )�����、( )和( )����,其中( )的沖突率最低。二�����、名詞解釋(每詞3分�,共15分)1. 程序局部性原理:2. 相關(guān):3. TLB:4. 通道處理機(jī):5. 動(dòng)態(tài)拓?fù)浣Y(jié)構(gòu)三、問(wèn)答題(每題5分���,共25分)1. 從計(jì)算機(jī)語(yǔ)言的角度���,把計(jì)算機(jī)系統(tǒng)層次按功能劃分哪幾級(jí)結(jié)構(gòu)? 2. 簡(jiǎn)述RISC的優(yōu)缺點(diǎn)�����。3. 在存儲(chǔ)層次中�,替換算法有哪幾種�?它們各有什么優(yōu)缺點(diǎn)����?4. 寫(xiě)策略主要有哪兩種���?它們各

3��、有什么優(yōu)點(diǎn)��? 5. 何謂多處理機(jī)的 Cache 一致性問(wèn)題�����,并簡(jiǎn)述出現(xiàn)這種問(wèn)題的原因��。四�����、計(jì)算題 (共25分)1. (12分)假設(shè)系統(tǒng)某一部件的處理速度加快 9 倍���,但該部件的原處理時(shí)間僅為整個(gè)運(yùn)行時(shí)間的 45% ,則采用加快措施后能使整個(gè)系統(tǒng)的性能提高多少���?如果部件改進(jìn)后獲得的加速比變?yōu)?SP=5.5 �����,問(wèn)改進(jìn)前的執(zhí)行時(shí)間占改進(jìn)后的百分比是多少����?2.(13分)已知一個(gè)Cache共有4個(gè)塊,每個(gè)塊大小為4個(gè)字����。采用直接映像方式,假設(shè)該Cache的缺失代價(jià)為8個(gè)時(shí)鐘周期�����。初始時(shí)Cache為空��,當(dāng)程序執(zhí)行過(guò)程中訪存的字地址序列為0,7,12,9,16,8,17,0,12,2時(shí),(1)試計(jì)算Cach

4���、e的命中率���。(2)計(jì)算Cache缺失(不命中)代價(jià)。五��、敘述題(15分)試從多角度簡(jiǎn)述 Cache存儲(chǔ)系統(tǒng)層次與虛擬存儲(chǔ)系統(tǒng)層次的區(qū)別。計(jì)算機(jī)系統(tǒng)結(jié)構(gòu)答案一��、填空題(每空一分��,共20分)1. SISD 單指令流單數(shù)據(jù)流 SIMD單指令流多數(shù)據(jù)流 MISD多指令流單數(shù)據(jù)流 MIMD多指令流多數(shù)據(jù)流2. 結(jié)構(gòu)沖突����、 數(shù)據(jù)沖突����、 控制沖突3. 吞吐量、 加速比�����、 效率4. 容量�、 速度、 價(jià)格 5. 水平處理����、 垂直處理、 分組處理6. 直接映象�����、 組相連映象、 全相連映象�����、 全相連映象二��、名詞解釋(每詞3分���,共15分)1. 程序執(zhí)行時(shí)所訪問(wèn)的存儲(chǔ)器地址分布不是隨機(jī)的�����,而是相對(duì)地簇聚����。程序往往重復(fù)使

5、用它剛剛使用過(guò)的數(shù)據(jù)和指令。2. 兩條指令之間存在某種依賴關(guān)系�����。如果兩條指令相關(guān)���,則它們就有可能不能在流水線中重疊執(zhí)行或者只能部分重疊執(zhí)行。3. 地址變換緩沖器����,是一個(gè)專用的高速緩沖器��,用于存放近期經(jīng)常使用的頁(yè)表項(xiàng)�,其內(nèi)容是頁(yè)表部分內(nèi)容的一個(gè)副本���。4. 能夠執(zhí)行有限I/O指令����,并且能夠被多臺(tái)外圍設(shè)備共享的小型DMA專用處理機(jī)���。5. 根據(jù)需要設(shè)置互連網(wǎng)絡(luò)中的開(kāi)關(guān),從而對(duì)結(jié)點(diǎn)之間的連接通路進(jìn)行重新組合���,實(shí)現(xiàn)所要求的通信模式��。三���、問(wèn)答題(每題5分,共15分)1. 2. 優(yōu)點(diǎn):(1)簡(jiǎn)化了指令系統(tǒng)的設(shè)計(jì)�����,適合VLSI的實(shí)現(xiàn)。 (2)提高了機(jī)器的執(zhí)行速度和效率��。 (3)降低了設(shè)計(jì)成本�����,提高了系統(tǒng)的可靠性

6����、。 (4)可直接支持高級(jí)語(yǔ)言的實(shí)現(xiàn)���,簡(jiǎn)化了編譯程序的設(shè)計(jì)����。缺點(diǎn):(1)由于指令少�,使原在CISI上的單一指令完成的某些復(fù)雜功能現(xiàn)在要用多條RISC指令才能完成,加重了 匯編語(yǔ)言程序的設(shè)計(jì)��。 (2)對(duì)浮點(diǎn)運(yùn)算執(zhí)行和虛擬存儲(chǔ)器的支持雖有很大加強(qiáng)��,但仍顯得不足�。 (3)RISC機(jī)器的編譯程序比CISC的難寫(xiě)。 3. (1)隨機(jī)法:簡(jiǎn)單��、易于用硬件實(shí)現(xiàn),但這種方法沒(méi)有考慮Cache塊過(guò)去被使用的情況�,反映不了程序的局部性,所以其失效率比LRU的高����。(2)先進(jìn)先出法:容易實(shí)現(xiàn)。它雖然利用了同一組中各塊進(jìn)入Cache的順序這一“歷史”信息���,但還是不能正確地反映程序的局部性�。(3)最近最少使用法LRU:失效

7�����、率最低����。但是LRU比較復(fù)雜���,硬件實(shí)現(xiàn)比較困難�。4. (1)寫(xiě)直達(dá)法:易于實(shí)現(xiàn)���,而且下一級(jí)存儲(chǔ)器中的數(shù)據(jù)總是最新的��。(2)寫(xiě)回法:速度快����,寫(xiě)操作能以Cache存儲(chǔ)器的速度進(jìn)行。而且對(duì)于同一單元的多個(gè)寫(xiě)最后只需一次寫(xiě)回下一級(jí)存儲(chǔ)器����,有些“寫(xiě)”只到達(dá)Cache,不到達(dá)主存���,因而所使用的存儲(chǔ)器頻帶較低�。5. 在多處理機(jī)系統(tǒng)中的私有 Cache 會(huì)引起 Cache 中的內(nèi)容相互之間以及共享存儲(chǔ)器之間互不相同的問(wèn)題�,稱為多處理機(jī)的 Cache 一致性問(wèn)題。出現(xiàn) Cache 一致性問(wèn)題的原因主要有如下兩點(diǎn):(1)Cache的引進(jìn)對(duì)IO操作產(chǎn)生了一致性問(wèn)題��,因?yàn)镃ache中的內(nèi)容可能與由IO子系統(tǒng)輸入輸出形成

8�����、的存儲(chǔ)器對(duì)應(yīng)部分的內(nèi)容不同����。即:I/O 傳輸所造成的數(shù)據(jù)不一致性。(2)對(duì)共享數(shù)據(jù),不同處理器的Cache都保存有對(duì)應(yīng)存儲(chǔ)器單元的內(nèi)容����,因而在操作中就可能產(chǎn)生數(shù)據(jù)的不一致。即:共享可寫(xiě)數(shù)據(jù)引起的不一致性�。第四題:計(jì)算題(共25分)1.(12分)(1)由題意可知,F(xiàn)e=0.45�,Se=9,代入公式: Sp = = = = = 1.56(2)根據(jù)題意有 Sp = = 5.5 由此可得 Fe = 91%2. (13分)字地址流進(jìn)入cache時(shí)工作情況: 時(shí)間12345678910字地址流07129168170122塊00000161617002塊1777777777塊29988888塊31212121212121212 裝入裝入裝入裝入替換替換替換替換命中替換在上表中�����,共有10個(gè)時(shí)刻����,只有時(shí)刻9命中,所以命中率1/10=10% (2) 缺失代價(jià)9872個(gè)時(shí)鐘周期第五題���、(共15分) 存儲(chǔ)層次比較項(xiàng)目“Cache-主存”層次“主存-輔存”層次目的為了彌補(bǔ)主存速度的不足為了彌補(bǔ)主存容量的不足存儲(chǔ)管理的實(shí)現(xiàn)全部由專用硬件實(shí)現(xiàn)主要由軟件實(shí)現(xiàn)訪問(wèn)速度的比值(第一級(jí)比第二級(jí))幾比一幾萬(wàn)比一典型的塊(頁(yè))大小幾十個(gè)字節(jié)幾百到幾千個(gè)字節(jié)CPU對(duì)第二級(jí)的訪問(wèn)方式可直接訪問(wèn)均通過(guò)第一級(jí)不命中時(shí)CPU是否切換不切換切換到其他進(jìn)程【精品文檔】第 2 頁(yè)

《計(jì)算機(jī)系統(tǒng)結(jié)構(gòu)》綜合自測(cè)題1

《計(jì)算機(jī)系統(tǒng)結(jié)構(gòu)》綜合自測(cè)題1